www.DRTLonline.com

## Physical, Electrical and Environmental Testing

Military Aerospace Communications Industrial Medical

ISDARC CHEES

DYNAMIC RESEARCH AND TESTING LABORATORIES, LLC

A Member of the IEC Electronics Family of Companies

### **Overview of Risk Mitigation Testing – Electrical**

ERAI Conference - April 18 & 19, 2013 Clifton Aldridge Laboratory Manager

## **Dynamic Research and Testing Laboratories, LLC**

Dynamic Research and Testing Laboratories, LLC is located in Albuquerque New Mexico. The Laboratory is within the Electronic Contract Manufacturer "IEC Electronics"

# **DRTL Organizational Chart**

Mark Northrup (Director of Laboratory)

Clifton Aldridge (Laboratory Manager) Jodi Wahl (Marketing Coordinator)

Holly Connelly (Administrative Specialist)

> Teri Kovaleski (Human Resources)

Chris Hoover (Quality Assurance)

Christine Glomski (Internal Auditor)

Karin Zimmerer (Document Control)

# **DRTL Organizational Chart**

Mark Northrup (Director of Laboratory)

Clifton Aldridge (Laboratory Manager) Rachel Garcia (Device Analyst II)

James Taylor (Failure Analysis Engineer)

Tony James (Failure Analysis Engineer)

JR Lucero (Device Technician)

Robert Perea (Device Technician)

Nabahe "Bo" Tewawina (Device Technician)

## **Dynamic Research and Testing Laboratories, LLC**

#### Navigating the Electrical Test Requirements When Procuring from Non-OCMs

### **Current Specifications**

AS5553 Fraudulent/Counterfeit Electronic Parts; Avoidance, Detection, Mitigation, and Disposition

AS6081 Fraudulent/Counterfeit Electronic Parts; Avoidance,

Detection, Mitigation, and Disposition – Distributors

AS6171 (Not Released) Test Methods Standard; General Requirements, Suspect/Counterfeit Electrical, Electronic, and Electromechanical Parts

CCAP-101 Counterfeit Components Avoidance Program Certification

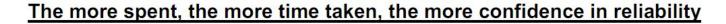

**TB-0003** Counterfeit Parts & Materials Risk Mitigation

GIFAS 5052 208 Guide for managing electronic component sourcing through non-franchised distributors. Preventing fraud and counterfeiting.

DYNAMIC RESEARCH AND TESTING LABORATORIES, LLC DRTL AMember of the IEC Electronics Family of Companies

- AS5553 Fraudulent & Counterfeit Electronic Parts

- Avoidance, Detection, Mitigation, and Disposition

#### E.1.10 Electrical Testing

Comprehensive electrical testing should be performed on all parts, across the full temperature range as per the parts' specification, in facilities with test equipment and test engineering expertise suitable for the specific part type. The acquiring activity should approve all test facilities and test methodologies. This test may be life limiting.

#### E.1.11 Burn-In

Pre Burn-In and Post Burn-In electrical testing should be performed on all parts using the criteria as defined in the applicable part specification. The steps involved in performing burn-in test are described below. This test may be life limiting.

- a. Pre Burn-In Electrical Performance Testing Parts should undergo comprehensive electrical testing to the applicable performance data sheet.

- b. Burn-In Parts (100%) should undergo a powered burn-in at the component's/part's maximum rated temperature.

- c. Post Burn-In Electrical Performance Testing Parts should undergo comprehensive electrical testing to the applicable performance data sheet.

- AS6081 Fraudulent & Counterfeit Electronic Parts

- Avoidance, Detection, Mitigation, and Disposition Distributors

#### C.3 ELECTRICAL TESTING

Comprehensive electrical testing should be performed on all parts in a facility with test equipment and test engineering expertise suitable for the specific part type. The Customer should approve all test facilities and test methodologies.

#### C.4 BURN-IN

Pre Burn-In and Post Burn-In electrical testing should be performed on all parts. The steps involved in performing burn-in test are described below.

- a. Pre Burn-In Electrical Performance Testing Parts should undergo comprehensive electrical testing to the applicable performance data sheet.

- b. Burn-In Parts (100%) should undergo a powered burn-in at the part's maximum rated temperature.

- c. Post Burn-In Electrical Performance Testing Parts should undergo comprehensive electrical testing to the applicable performance data sheet.

AS6171 (Not Released) Test Methods Standard; General Requirements, Suspect/Counterfeit Electrical, Electronic, and Electromechanical Parts

- > AS6171 provides further detail to the electrical test requirements

- 3.4.1.6 Electrical –AS6171Test Method VI

- Such electrical testing shall be performed using appropriate requirements as specified in related SMDs, MIL-PRFs, manufacturer datasheets or customer supplied requirement documents.

- Sampling plan calls for 116devices/c=0 tested with no failures allowed. This gives a 90 percent confidence that the percentage failures is at most 2%.

- The type and extent of electrical testing is so complex to try to screen-out counterfeit parts that it is the responsibility of the User Engineer to make the determination of the specific test requirements that shall be documented in a Test Requirements document that shall become part of a Statement of Work (SOW).

- The minimum level of electrical testing for the Low Risk Level is defined as the DC Test for Active Devices and Value Measurement for Passive Devices. At the minimum level the tests shall be performed at ambient temperature

- Detailed guidance provided in AS6171 TEST METHOD VI

#### AS6171 (Not Released) Test Methods Standard; General Requirements, Suspect/Counterfeit Electrical, Electronic, and Electromechanical Parts

| + |                           |                                                                   | E DEVICES KEY ELECTRICAL PARAMETERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |

|---|---------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|   | PART<br>CATEGORY          | ТҮРЕ                                                              | KEY ELECTRICAL PARAMETERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MIL STD/SPEC          |

|   | Microcircuit -<br>Linear  | (Generic LM111                                                    | Input offset voltage & current, raised input offset<br>voltage & current, input bias, collector output<br>voltage (strobed), common mode rejection, low level<br>output voltage, input & output leakage current, pos.<br>& neg. supply current, temp. coeff. Of input offset V<br>& I, Output short circuit current, adj. for input offset<br>volt., volt. Gain, response time(collector output)                                                                                                            | DLA SMD<br>5962-00524 |

|   |                           | Operational<br>Amplifiers, Quad,<br>Precision<br>(Generic OP484)  | Input offset voltage; Average input offset voltage;<br>Input offset current; Input bias current; Common<br>mode rejection ratio; Power supply rejection ratio;<br>Output high voltage; Output Iow voltage; Large<br>signal voltage gain; Supply current; Slew rate                                                                                                                                                                                                                                          | DLA SMD<br>5962-00517 |

|   |                           | (Generic AD904                                                    | Vcc supply current; Power dissipation; Power supply<br>rejection ratio; Offset error; Gain error; Input voltage<br>range; Input logic high & low voltage; Input logic<br>high & low current; Output logic high & low voltage;<br>Differential non-linearity; Signal to noise ratio; Signal<br>to noise and distortion ratio; Worst spur ratio                                                                                                                                                               | DLA SMD<br>5962-02538 |

|   | Microcircuit -<br>Digital | Octal Bus<br>Transceiver and<br>Register<br>(Generic<br>54BCT646) | High & low level output voltage; Input clamp voltage;<br>High & low level input current; Short-circuit output<br>current, Supply currents; Functional tests to verify<br>the Truth table of the SMD; Max. clock frequency;<br>Propagation delay times                                                                                                                                                                                                                                                       | DLA SMD<br>5962-91555 |

|   | Microcircuit -<br>Memory  | SRAM (Static<br>Random Access<br>Memory), 2M x 8 Bit              | Output high & low voltage; Input and output leakage<br>current; Supply currents, Data retention current;<br>Propagation delay times (Address/Chip<br>Enable/Output Enable to data valid, including the<br>write cycle set-up parameters); Functional tests to<br>verify proper operation of SRAM as specified in<br>Appendix A of the SMD (Check all memory cells by<br>using the following algorithms:<br>Checkerboard/checkerboard/ bar, March, XY March<br>CE deselect checkerboard/ checkerboard/bar or | DLA SMD<br>5962-08219 |

RESEARCH

#### CCAP-101 COUNTERFEIT COMPONENTS AVOIDANCE PROGRAM, CERTIFICATION

#### 4.9.6 Passive components

All unmarked passive components (both Level A & B) or not contained in OCM original and verified packaging shall be sample tested, 30 pcs/1000 components for parameters specified below.

The tests shall be in accordance with OCM data sheets or military specifications as applicable.

A. Capacitors:

Capacitance and tolerance at 25 <sup>o</sup>C and min/max temp DWV Dissipation factor as applicable ESR (Electrolytics only)

B. Inductors:

Inductance over or within specified frequency and temperature range Q Series resistance

C. Resistors:

Resistance and tolerance at 25 <sup>o</sup>C and min/max temp. Temperature coefficient

D. Other Passives Applicable parameters

**TB-0003 Counterfeit Parts & Materials Risk Mitigation**

DRTL

RESEARCH

GIFAS 5052 208 Guide for managing electronic component sourcing through non-franchised distributors. Preventing fraud and counterfeiting

| THE FRENCH AEROSPACE INDUSTRIES ASSOCIATION |

|---------------------------------------------|

|                                             |

E. Electrical tests

This is a test conducted at room temperature on a per unit or sampling basis, depending on the inspection lot and/or package size, in order to verify the electrical characteristics specified by the manufacturer. This test may be accompanied by tests at operating temperature and life testing, depending on the level of quality required and the criticality of the application.

All electrical and physical tests and analyses must be performed by an internal or outside specialist and recognized laboratory.

GIFAS/5052/2008

When did "Requirement Specifications" become "Guidance Documents" leaving interpretation to the operator, tester, or user ( e.g., Technician, Component Engineer, Program Manager, etc.) ?

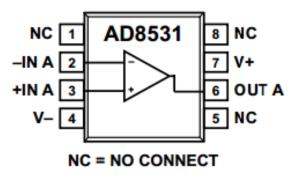

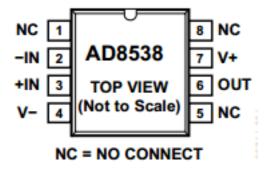

> Basic building block devices may be more attractive for counterfeiting

- Examples : Op-amps, comparators, low level logic, ADCs, DACs, MOSFETs, Diodes, Capacitors, Resistors...

- Pros for the counterfeiter

- Larger selection of pin for pin capable devices to substitute

- Typical designs may have large margins allowing of passage of system level checks

- Cons for the counterfeiter

- Typically lower cost devices

- May need large volume for same price point

- Complex devices (FPGAs, CPU, SIC...)

- Xilinx, Motorola, and Intel ?

- Have system security features in the chip (e.g., embedded at the die level) to difficult to repeat or defeat?

- Most likely will not pass the board assembly system level electrical verification/functional testing?

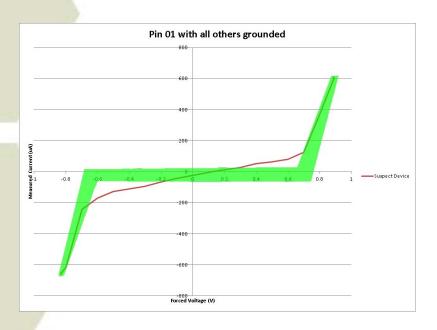

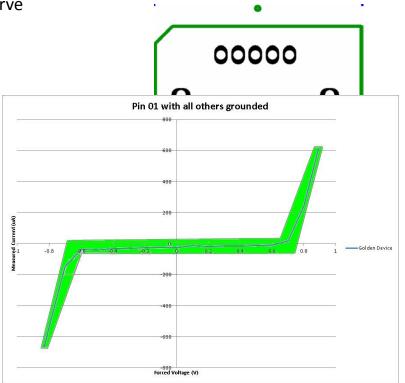

## **Going Beyond Simple Pin to Pin Testing**

- Obtain Current vs Voltage (IV) curve for golden device

- Software defines passing limits around the golden device curve

- Software builds a mask around the golden device curve

- Suspect devices IV curves obtained

- Suspect devices tested in comparison to the golden device

- Suspect devices tested even with slight damage can be detected.

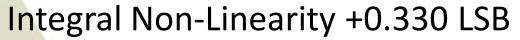

# **Full Functional Testing**

- Key Parameters may need to be tested in order to validate the functionality of the device under test.

- Devices having the same basic function may not have the same over all performance.

- Degraded performance can reduce over all design margins and system performance.

| TEST     |                                        | _READING                                             | Cust P/N: :<br>Slot = 3                                                | MAX                                    | P/F"                             |                            |

|----------|----------------------------------------|------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------|----------------------------------|----------------------------|

| Iccq     | <br>A                                  | +984.432uA                                           |                                                                        | +2.000mA                               | "<br>P"                          |                            |

| IOut     | A                                      |                                                      | +5.000mA                                                               | +20.000mA                              | P"                               |                            |

| tSett Er | rB1_A                                  | +800.000nSec                                         | 2                                                                      | +1.500uSec                             | P"                               |                            |

| INL/LE   | A                                      |                                                      |                                                                        | +0.500 LSB                             | P"                               |                            |

| DNL      | Ā                                      | +0.062 LSB                                           |                                                                        | +0.500 LSB                             | P"                               |                            |

| Gai      | Ā                                      | +0.008 %FSR                                          |                                                                        | +0.400 %FS                             | R P"                             |                            |

| I        | A                                      | +180.576pA                                           |                                                                        | +1.000uA                               | p"                               |                            |

| 7 /      | A                                      | +175.418pA                                           |                                                                        | +1.000uA                               | P"                               |                            |

|          | - <u>-</u> A                           | +174.181pA                                           |                                                                        | +1.000uA                               | -<br>P"                          |                            |

|          |                                        | 11/11/01/01                                          |                                                                        | 11.000000                              |                                  |                            |

|          |                                        |                                                      | t) Traveler# 1200                                                      |                                        |                                  |                            |

| 41       | CUSTO                                  | OMER: IEC ELECT                                      | RONICS ABQ<br>2 S/N = 5                                                | Cust P/N: : SI                         | D-MP1230ABN-Q                    |                            |

| Iil      | Test                                   | Date 10/18/201                                       | .2  S/N = 5                                                            | Slot = 2                               | Temperature =                    | -40"                       |

|          |                                        |                                                      |                                                                        |                                        |                                  |                            |

| Iil      | ###                                    | TEST                                                 | READING                                                                | MIN                                    | MAX                              | P/F"                       |

| Iih      |                                        |                                                      |                                                                        |                                        |                                  | "                          |

| Iih      | 1                                      | Iccq _A                                              | +513.493uA                                                             |                                        | +2.000mA                         | P"                         |

| Iih      | 2                                      | IOut A                                               | +10.267mA                                                              | +5.000mA                               | +20.000mA                        | P"                         |

| Iih      | 3                                      |                                                      | A +700.000nSec                                                         |                                        | +1.500uSec                       | P"                         |

| Iih      | 4                                      | INL/LE A                                             | +2.174 LSB                                                             |                                        | +0.500 LSB                       | FAIL                       |

| Iih      | 5                                      | DNL/DLE A<br>Gain Err A                              | .002 LSB                                                               |                                        | +0.500 LSB                       | P"                         |

| Iih      |                                        | Gain Err 🦯                                           | 053 %FSR<br>819pA                                                      |                                        | +0.400 %FSR                      | P"                         |

| Iih      | 7                                      | Gain Err<br>Iil<br>Iil A<br>Iil A                    | 819pA                                                                  |                                        | +1.000uA                         | P"                         |

| Vih      | 8                                      | Iil _A                                               | 4.964pA                                                                |                                        | +1.000uA                         | P"                         |

| Vih      | 9                                      | Iil _P                                               | 14.383pA                                                               |                                        | +1.000uA                         | P"                         |

| Vih      | 10                                     | 111 _4                                               | /3.594pA                                                               |                                        | +1.000uA                         | P"                         |

|          | 11                                     | Iil _                                                | 72.218pA                                                               |                                        | +1.000uA                         | P"                         |

| Vih      | 12                                     | Iil -                                                | 73.520pA                                                               |                                        | +1.000uA                         | P"                         |

| Vil      | 13                                     | Iil -                                                | .72.306pA                                                              |                                        | +1.000uA                         | P"                         |

| Vil      | 14<br>15                               | Iil .                                                | 175.092pA                                                              |                                        | +1.000uA                         | P"<br>P"                   |

| Vil      | 15                                     | Iih<br>Iih                                           | 124.525pA<br>140.526pA                                                 |                                        | +1.000uA<br>+1.000uA             | P"                         |

| Vil      | 17                                     | lin<br>Iih                                           | 140.526pA<br>141.174pA                                                 |                                        | +1.000uA<br>+1.000uA             | P"                         |

|          | -18                                    | Iin<br>Iih                                           | -                                                                      |                                        |                                  | P"                         |

|          | 19                                     | Iin<br>Iih                                           | +147.421pA<br>+149.424pA                                               |                                        | +1.000uA<br>+1.000uA             | P"                         |

|          |                                        | Iih                                                  | +149.424pA<br>+150.086pA                                               |                                        | +1.000uA<br>+1.000uA             | P"                         |

|          |                                        |                                                      |                                                                        |                                        | +1.000uA                         | p"                         |

|          | 20                                     |                                                      |                                                                        |                                        |                                  |                            |

|          | 21                                     | Iih                                                  | +156.224pA<br>+152.150pA                                               |                                        | +1 000112                        | D"                         |

|          | 21<br>22                               | Iih<br>Iih                                           | +152.150pA                                                             |                                        | +1.000uA<br>+2.400 V             | P"                         |

|          | 21<br>22<br>23                         | Iih<br>Iih<br>Vih                                    | +152.150pA<br>+1.804 V                                                 |                                        | +2.400 V                         | P"                         |

|          | 21<br>22<br>23<br>24                   | Iih<br>Iih<br>Vih<br>Vih                             | +152.150pA<br>+1.804 V<br>+1.765 V                                     |                                        | +2.400 V<br>+2.400 V             | P"<br>P"                   |

|          | 21<br>22<br>23<br>24<br>25             | Iih<br>Iih<br>Vih<br>Vih<br>Vih                      | +152.150pA<br>+1.804 V<br>+1.765 V<br>+1.785 V                         |                                        | +2.400 V<br>+2.400 V<br>+2.400 V | P"<br>P"<br>P"             |

|          | 21<br>22<br>23<br>24                   | Iih<br>Iih<br>Vih<br>Vih<br>Vih<br>Vih               | +152.150pA<br>+1.804 V<br>+1.765 V<br>+1.785 V<br>+1.790 V             | +800.000mV                             | +2.400 V<br>+2.400 V             | P"<br>P"                   |

|          | 21<br>22<br>23<br>24<br>25<br>26<br>27 | Iih<br>Iih<br>Vih<br>Vih<br>Vih<br>Vih<br>Vih<br>Vih | +152.150pA<br>+1.804 V<br>+1.765 V<br>+1.785 V<br>+1.790 V<br>+1.248 V | +800.000mV<br>+800.000mV               | +2.400 V<br>+2.400 V<br>+2.400 V | P"<br>P"<br>P"<br>P"       |

|          | 21<br>22<br>23<br>24<br>25<br>26       | Iih<br>Iih<br>Vih<br>Vih<br>Vih<br>Vih               | +152.150pA<br>+1.804 V<br>+1.765 V<br>+1.785 V<br>+1.790 V             | +800.000mV<br>+800.000mV<br>+800.000mV | +2.400 V<br>+2.400 V<br>+2.400 V | P"<br>P"<br>P"<br>P"<br>P" |

## Integral Non-Linearity +2.174 LSB

19 20

21

# **Full Functional Testing**

|                                  |                    |       | (       | 27 (IRF540 | 5)  |       |         | Q8 (IRFR | 024) |        |

|----------------------------------|--------------------|-------|---------|------------|-----|-------|---------|----------|------|--------|

|                                  |                    |       | Suspect | Exemplar   | Li  | mits  | Suspect | Exemplar | L    | imits. |

| Test                             |                    | Units | SN 2148 | SN 1088    | Min | Max   | SN 2148 | SN 1088  | Min  | Max    |

| BVDSS                            |                    | V     | 114.4   | 113.6      | 100 |       | 64.1    | 67.6     | 55   |        |

| rdsON (17A and 10A respectively) | Initial            | ohms  | 0.047   | 0.051      |     | 0.077 | 0.053   | 0.066    |      | 0.075  |

| Vgsth                            |                    | V     | 2.57    | 2.74       | 2   | 4     | 1.66    | 2.78     | 2    | 4      |

|                                  |                    |       | (       | 27 (IRF540 | 5)  |       |         | Q8 (IRFR | 024) |        |

|                                  |                    |       | Suspect | Suspect    | Li  | mits  | Suspect | Suspect  | L    | imits. |

| Test                             |                    | Units | SN 6150 | SN 0151    | Min | Max   | SN 6150 | SN 0151  | Min  | Max    |

| BVDSS                            |                    | V     | 121.1   | 106.3      | 100 |       | 64.1    | 64.6     | 55   |        |

| rdsON (17A and 10A respectively) | Initial            | ohms  | 0.05    | 0.055      |     | 0.077 | 0.074   | 0.078    |      | 0.075  |

| Vgsth                            |                    | V     | 2.57    | 2.78       | 2   | 4     | 3.33    | 3.02     | 2    | 4      |

| BVDSS                            |                    | V     | 121.3   | 106.2      | 100 |       | 64.1    | 64.7     | 55   |        |

| rdsON (17A and 10A respectively) | Post HAST          | ohms  | 0.051   | 0.055      |     | 0.077 | 0.073   | 0.077    |      | 0.075  |

| Vgsth                            |                    | V     | 2.57    | 2.78       | 2   | 4     | 3.32    | 3.02     | 2    | 4      |

| BVDSS                            |                    | V     | 121     | 106.2      | 100 |       | 64.2    | 64.7     | 55   |        |

| rdsON (17A and 10A respectively) | Post Thermal Shock | ohms  | 0.051   | 0.054      |     | 0.077 | 0.074   | 0.078    |      | 0.075  |

| Vgsth                            |                    | V     | 2.57    | 2.77       | 2   | 4     | 3.33    | 3.02     | 2    | 4      |

BRTL

| S/N | Vz                      | I <sub>R</sub>         | V <sub>z</sub> for a 1N3000RB | I <sub>R</sub> for a 1N3000RB | 1 |

|-----|-------------------------|------------------------|-------------------------------|-------------------------------|---|

|     | 7.125 – 7.875 V         | 100 uA max.            | 58.9–65.1 V                   | 10uA max.                     |   |

|     | I <sub>R</sub> = 335 mA | V <sub>R</sub> = 5.7 V | I <sub>R</sub> = 40 mA        | V <sub>R</sub> = 47.1 V       |   |

| 1   | <1000V                  | 0.011 uA               |                               |                               |   |

| 2   | 59V @ 40 mA             | 144.6 uA               | 59V                           | 1710 uA                       |   |

|     |                         |                        |                               |                               |   |

|     |                         |                        |                               |                               |   |

|     |                         |                        |                               |                               |   |

|     |                         |                        |                               |                               |   |

**Comments:** SN 1 appears to be a switching power diode with a reverse breakdown of ~1200V. No signs of leakage or damage of the diode detected. SN 2 appears to be a 62V Zener diode. This diode appears to be a 1N3000RB, however would still fail the reverse current measurement for this device type as well.

Input Offset, Vos 25mV max Output Current 250mA Supply Current, Icc 1 mA

Input Offset, Vos 13uV max Output Current 25mA Supply Current, Icc 180 uA

# Summary of Electrical Test Issues

- Current risk mitigation standards are open to interpretation which breeds inconsistency across test facilities in actual test performed and costs.

- Paramount to understand end use (Avionics, Missile, Industrial, Medical)

- Completely define test requirements (DCs, Acs Functional, Over Temp).

- Best case is to have the user define important parameters to tested based on the functionality of the device or based on the requirements of the design

- The user may not have access to design information, however the test facility sould provide different options or levels based on the functionality of the device.

- Suggest read and record data be required for all parameters (data can be reviewed not just failing parameters). Industry Database?

- Recommendations?

## ISO 17025 Skill Set Model

| Skill Set Model                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                          | Compe                                                              | tency                                                    |                                                                                                     |                                                                                                               |                                                                    |                                                                                                                                                                                                                                                                                                                            |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| la ca                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                          | Expense                                                            | Hice                                                     |                                                                                                     |                                                                                                               |                                                                    | at or                                                                                                                                                                                                                                                                                                                      |        |

| Instruction-related review / training<br>les the related<br>= Instructions<br>= Checklists                                                                                                                                                                                                                                                                                      |                                                                                                                                                          | Training<br>On the<br>Observ<br>Test<br>Educat                     | Job Tri<br>ation                                         | anng                                                                                                | EXF<br>TR(<br>OJ)<br>OBS<br>TS<br>ED(                                                                         |                                                                    | Adindige CA Initiality Initiality Initiality Initiality Monter Methy Pending Skill Training Mover CH Completed Skill Training                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                 | Planned                                                                                                                                                  | Eval. Method                                                       | Evaluator                                                | Completed                                                                                           | Planned                                                                                                       | Eval. Method                                                       | Dynamic Research and Testing Laboratories – Business Instruct                                                                                                                                                                                                                                                              | ction  |

|                                                                                                                                                                                                                                                                                                                                                                                 | Dev                                                                                                                                                      | JR Lu                                                              | cero                                                     | er                                                                                                  |                                                                                                               | Rache                                                              | Document Title:                                                                                                                                                                                                                                                                                                            |        |

| Process                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                          |                                                                    |                                                          |                                                                                                     | -                                                                                                             | Device                                                             | DYNAMIC                                                                                                                                                                                                                                                                                                                    |        |

|                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                          |                                                                    |                                                          |                                                                                                     |                                                                                                               |                                                                    |                                                                                                                                                                                                                                                                                                                            |        |

| P-001, Testing Process                                                                                                                                                                                                                                                                                                                                                          | 11/30/11                                                                                                                                                 | 0.0                                                                | -                                                        |                                                                                                     |                                                                                                               |                                                                    | AND TESTING Pin to Pin Curve Trace                                                                                                                                                                                                                                                                                         |        |

| P-001, Testing Process<br>1-001, SEM Examination                                                                                                                                                                                                                                                                                                                                | 11/30/11                                                                                                                                                 | TLO<br>TLO                                                         |                                                          | 11/30/11                                                                                            | 8/2/11                                                                                                        | 1                                                                  | AND TESTING<br>LABORATORIES, LLC                                                                                                                                                                                                                                                                                           |        |

| 1-001, SEM Examination                                                                                                                                                                                                                                                                                                                                                          | 11/30/11                                                                                                                                                 | ол                                                                 | CA                                                       | 11/30/11                                                                                            | 1/30/12                                                                                                       | TRC                                                                | AND TESTING<br>LABORATORIES, LLC                                                                                                                                                                                                                                                                                           |        |

| 1-001, SEM Examination<br>1-002, Internal Examination<br>1-013, Olympus B/SO Leica M280 - Infinity<br>nera Operating Procedure                                                                                                                                                                                                                                                  |                                                                                                                                                          |                                                                    |                                                          |                                                                                                     | 1/30/12<br>8/2/11                                                                                             | TRC                                                                | AND TESTING<br>LABORATORIES, LLC<br>Document Number:                                                                                                                                                                                                                                                                       |        |

| 1-001, SEM Examination<br>1-002, Internal Examination<br>1-013, Olympus B/SD Leica M280 - Infinity<br>hera Operating Procedure<br>1-004, Wire Bond and Die Shear Test                                                                                                                                                                                                           | 11/30/11<br>11/30/11<br>11/30/11                                                                                                                         | τιο<br>τιο<br>τιο                                                  | CA<br>CA<br>CA                                           | 11/30/11<br>11/30/11<br>1/24/12                                                                     | 1/30/12<br>8/2/11<br>8/2/11                                                                                   | TRC<br>TRC<br>TRC                                                  | AND TESTING<br>LABORATORIES, LLC                                                                                                                                                                                                                                                                                           |        |

| 1001; SEM Examination<br>1002; Internal Examination<br>1013; Olympus B/SO Leica M280 - Infinity<br>nera Operating Procedure<br>1004; Wire Bond and Die Shear Test<br>ructions                                                                                                                                                                                                   | 11/30/11<br>11/30/11                                                                                                                                     | TLO<br>TLO                                                         | CA<br>CA                                                 | 11/30/11<br>11/30/11<br>1/24/12<br>11/30/11                                                         | 1/30/12<br>8/2/11<br>8/2/11<br>8/2/11                                                                         | TRC<br>TRC<br>TRC<br>TRC                                           | AND TESTING<br>LABORATORIES, LLC   Pin to Pin Curve Trace     Document Number:   TSTI-043, Rev C     Document Owner:   Approver(s):                                                                                                                                                                                        |        |

| 1001, SEM Examination<br>1002, Internal Examination<br>1013, Olympus B/SD Leica M280 - Infinity<br>nera Operating Procedure<br>1004, Wire Bond and Die Shear Test<br>ructions<br>1012, Wet Saw Operation                                                                                                                                                                        | 11/30/11<br>11/30/11<br>11/30/11<br>11/30/11                                                                                                             | τιο<br>τιο<br>τυο<br>τιο                                           | CA<br>CA<br>CA<br>CA                                     | 11/30/11<br>11/30/11<br>1/24/12                                                                     | 1/30/12<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11                                                               | TRC<br>TRC<br>TRC<br>TRC<br>TRC                                    | AND TESTING<br>LABORATORIES, LLC<br>Document Number:<br>TSTI-043, Rev C                                                                                                                                                                                                                                                    |        |

| 1001, SEM Examination<br>1002, Internal Examination<br>1013, Olympus B/SD Leica M280 - Infinity<br>nera Operating Procedure<br>1004, Wire Bond and Die Shear Test<br>ructions<br>1012, Wet Saw Operation<br>1014, Chemical Decapulation Instructions                                                                                                                            | 11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11                                                                                                 | τιο<br>τιο<br>τιο<br>τιο<br>τιο                                    | CA<br>CA<br>CA<br>CA                                     | 11/30/11<br>11/30/11<br>1/24/12<br>11/30/11<br>1/20/12                                              | 1/30/12<br>8/2/11<br>8/2/11<br>8/2/11                                                                         | TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC                      | AND TESTING<br>LABORATORIES, LLC   Pin to Pin Curve Trace     Document Number:   TSTI-043, Rev C     Document Owner:   Approver(s):                                                                                                                                                                                        |        |

| H001, SEM Examination<br>H002, Internal Examination<br>H013, Olympus B/SO Leica M280 - Infinity<br>hera Operating Procedure<br>H004, Wire Bond and Die Shear Test<br>ructions<br>H012, Wet Saw Operation<br>H014, Chemical Decapulation Instructions<br>H015, Sample Mounting Instructions                                                                                      | 11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11                                                                                     | τιο<br>τιο<br>τιο<br>τιο<br>τιο<br>τιο                             | CA<br>CA<br>CA<br>CA<br>CA                               | 11/30/11<br>11/30/11<br>1/24/12<br>11/30/11<br>1/20/12<br>11/30/11                                  | 1/30/12<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11                                                     | TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC               | AND TESTING<br>LABORATORIES, LLC   Pin to Pin Curve Trace     Document Number:   TSTI-043, Rev C     Document Owner:   Approver(s):     Jimmy Lucero   Clifton Aldridge                                                                                                                                                    |        |

| 1001, SEM Examination<br>1002, Internal Examination<br>1013, Olympus BXSD Leica M280 - Infinity<br>nera Operating Procedure<br>1004, Wire Bond and Die Shear Test<br>ructions<br>1012, Wet Saw Operation<br>1014, Chemical Decapulation Instructions<br>1015, Sample Mounting Instructions<br>1016, Solderability Testing                                                       | 11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11                                                             | τιο<br>τιο<br>τιο<br>τιο<br>τιο<br>τιο<br>τιο<br>τιο               | CA<br>CA<br>CA<br>CA<br>CA<br>CA                         | 11/30/11<br>11/30/11<br>1/24/12<br>11/30/11<br>1/20/12<br>11/30/11<br>1/24/12                       | 1/30/12<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11                                           | TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC | AND TESTING<br>LABORATORIES, LLC   Pin to Pin Curve Trace     Document Number:   TSTI-043, Rev C     Document Owner:   Approver(s):     Jimmy Lucero   Clifton Aldridge                                                                                                                                                    |        |

| 1-001, SEM Examination<br>1-002, Internal Examination<br>1-013, Olympus BiSSD Leica M280 - Infinity<br>nera Operating Procedure<br>1-004, Wire Bond and Die Shear Test<br>ructions<br>10-012, Wet Saw Operation<br>10-014, Chemical Decapulation Instructions<br>10-015, Sample Mounting Instructions<br>10-016, Solderability Testing<br>10-005, XRF                           | 11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>1/24/12<br>1/24/12                                                   | т.0<br>т.0<br>т.0<br>т.0<br>т.0<br>т.0<br>т.0<br>т.0               | CA<br>CA<br>CA<br>CA<br>CA<br>CA<br>CA                   | 11/30/11<br>11/30/11<br>1/24/12<br>11/30/11<br>1/20/12<br>11/30/11<br>1/24/12<br>1/24/12            | 1/30/12<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>6/15/12                      | TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC | AND TESTING<br>LABORATORIES, LLC   Pin to Pin Curve Trace     Document Owner:   Document Owner:     Jimmy Lucero   Approver(s):<br>Clifton Aldridge     Parent Document:   Notify of Changes:                                                                                                                              |        |

| 1001, SEM Examination<br>1002, Internal Examination<br>1013, Olympus B/SD Leica M280 - Infinity<br>1004, Wire Bond and Die Shear Test<br>1004, Wire Bond and Die Shear Test<br>1012, Wet Saw Operation<br>1014, Chemical Decapulation Instructions<br>1015, Sample Mounting Instructions<br>1016, Solderability Testing<br>1005, XRF<br>10006, Radiographic / %-ray Examination | 11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>1/24/12<br>1/24/12                                                   | 0.1<br>0.1<br>0.1<br>0.1<br>0.1<br>0.1<br>0.1<br>0.1<br>0.1<br>0.1 | CA<br>CA<br>CA<br>CA<br>CA<br>CA<br>CA<br>CA<br>CA       | 11/30/11<br>11/30/11<br>1/24/12<br>11/30/11<br>1/20/12<br>11/30/11<br>1/24/12<br>1/24/12<br>1/24/12 | 1/30/12<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>6/15/12<br>3/15/12           | TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC | AND TESTING<br>LABORATORIES, LLC   Pin to Pin Curve Trace     Document Owner:   TSTI-043, Rev C     Jimmy Lucero   Approver(s):<br>Clifton Aldridge     Backup Owner:   Clifton Aldridge     Parent Document:<br>TSTP-001, Testing Process   Notify of Changes:<br>All Dynamic Research and Testing Laboratories Employees |        |

| 1-001, SEM Examination<br>1-002, Internal Examination<br>1-013, Olympus BXSD Leica M280 - Infinity<br>nera Operating Procedure<br>1-004, Wire Bond and Die Shear Test<br>ructions<br>1-012, Wet Saw Operation<br>1-012, Wet Saw Operation<br>1-014, Chemical Decapulation Instructions<br>1-015, Sample Mounting Instructions<br>1-016, Solderability Testing                   | 11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11<br>11/30/11 | 0.1<br>0.1<br>0.1<br>0.1<br>0.1<br>0.1<br>0.1<br>0.1<br>0.1<br>0.1 | CA<br>CA<br>CA<br>CA<br>CA<br>CA<br>CA<br>CA<br>CA<br>CA | 11/30/11<br>11/30/11<br>1/24/12<br>11/30/11<br>1/20/12<br>11/30/11<br>1/24/12<br>1/24/12<br>1/24/12 | 1/30/12<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>8/2/11<br>6/15/12<br>3/15/12<br>8/2/11 | TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC<br>TRC | AND TESTING<br>LABORATORIES, LLC   Pin to Pin Curve Trace     Document Owner:   Document Owner:     Jimmy Lucero   Approver(s):<br>Clifton Aldridge     Parent Document:   Notify of Changes:                                                                                                                              | klist; |

A Member of the IEC Electronics Family of Companie

# **DRTL and IEC Electronics**

A Momber of the IEC Electronics Family of Companies

DYNAMIC

# **DRTL Capabilities**

### **Dynamic Research and Testing Laboratories (DRTL)**

- Component Risk Mitigation

- Destructive Physical Analysis

- Failure Analysis

- Parts Screening

- Product Qualifications

- Material Qualifications

- Consulting Services

- ➢ ISO 17025 Certified

Our staff offers highly respected technical expertise, personable service, and quick response.

## Can You Afford Not To have A Risk Mitigation Strategy ?